- 您现在的位置:买卖IC网 > Sheet目录1253 > XGBE-XGXS-O4-N2 (Lattice Semiconductor Corporation)IP CORE 10GBE ETHERNET XGXS

�� �

�

Lattice� Semiconductor�

�10Gb� Ethernet� XGXS� IP� Core� User’s� Guide�

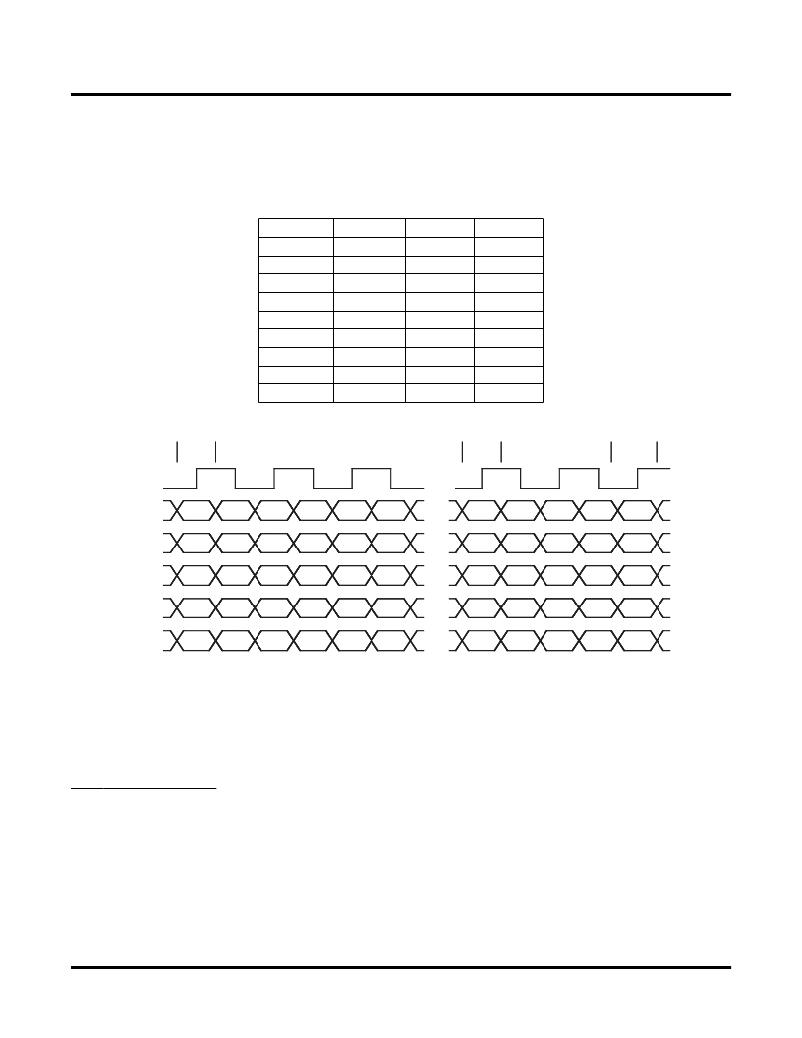

�The� CRPAT� packet� sequence� is� generated� by� the� XGMII� packet� generator� and� is� mapped� into� appropriate� XAUI�

�code� groups� by� the� XGXS� TX� encoder� block.� The� CRPAT� frame� is� mapped� to� the� XAUI� lanes� as� shown� in� Table� 6.�

�The� packet� generator� output� may� also� be� loop� back� to� the� XGMII� RX� interface.� Figure� 8� shows� how� CRPAT� packets�

�are� mapped� to� the� 32-bit� XGMII� data� bus.� Each� byte� lane� corresponds� to� a� XAUI� lane� as� described� in� Table� 1.� All�

�values� shown� in� the� ?� gure� are� in� hexadecimal.�

�Table� 6.� Lane� Mapping� of� Frame� Data�

�Lane� 0�

�SOP� (FB)�

�P4� (55)�

�D1� (BE)�

�—�

�Lane� 1�

�P1� (55)�

�P5� (55)�

�D2� (BE)�

�—�

�Lane� 2�

�P2� (55)�

�P6� (55)�

�D3� (BE)�

�—�

�Lane� 3�

�P3� (55)�

�SFD� (D5)�

�D4� (BE)�

�—�

�D1485� (59)�

�D1486� (59)� D1487� (59)� D1488� (59)�

�CRC1� (F8)�

�EOP� (FD)�

�Idle� (07)�

�Idle� (07)�

�CRC2� (79)�

�Idle� (07)�

�Idle� (07)�

�Idle� (07)�

�CRC3� (05)�

�Idle� (07)�

�Idle� (07)�

�Idle� (07)�

�CRC4� (59)�

�Idle� (07)�

�Idle� (07)�

�Idle� (07)�

�Figure� 8.� Packet� Transmission� at� the� XGMII� Interface�

�Start� t�

�186� cycles� of� data�

�CRC�

�IPG�

�Start�

�tx_clk�

�----�

�txd[7:0]�

�FB�

�55�

�BE�

�D7�

�23�

�47�

�----�

�F8�

�FD�

�07�

�07�

�FB�

�txd[15:8]�

�55�

�55�

�BE�

�D7�

�23�

�47�

�----�

�79�

�07�

�07�

�07�

�55�

�txd[23:16]�

�55�

�55�

�BE�

�D7�

�23�

�47�

�----�

�05�

�07�

�07�

�07�

�55�

�txd[31:24]�

�55�

�D5�

�BE�

�D7�

�23�

�47�

�----�

�59�

�07�

�07�

�07�

�55�

�txc[3:0]�

�0x1�

�0x0�

�0x0�

�0x0�

�0x0�

�0x0�

�----�

�0x0�

�0xF�

�0xF�

�0xF�

�0x1�

�Continuous� Jitter� Test� Pattern� (CJPAT)�

�The� purpose� of� the� CJPAT� capability� is� to� provide� a� data� pattern� that� exposes� a� receiver’s� CDR� to� large� instanta-�

�neous� phase� jumps.� The� pattern� alternates� repeating� low� transition� density� patterns� with� repeating� high� transition�

�density� patterns.� The� CJPAT� pattern� consists� of� a� continuous� stream� of� identical� packets� separated� by� a� minimum�

�IPG.� Each� packet� consists� of� eight� bytes� of� START/PREAMBLE/� SFD� followed� by� 1504� data� bytes� followed� by� four�

�CRC� bytes� followed� by� a� minimum� of� 12� bytes� of� IPG.� The� speci� ?� c� pattern� is� as� follows:�

�START/PREAMBLE/SFD� (same� as� CRPAT)�

�Data� bytes:�

�0B� (lane� 0)�

�7E� (for� 3� bytes� -� lanes� 1,� 2� and� 3)�

�7E� (for� 524� bytes)�

�F4� (for� 4� bytes)�

�EB� (for� 4� bytes)�

�F4� (for� 4� bytes)�

�EB� (for� 4� bytes)�

�F4� (for� 4� bytes)�

�12�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XM2D-0901

CONNECTOR

XM2D-3701

CONNECTOR

XM4M-2432-1312

CONN DVI 24POS 1.5A 40V DIGITAL

XM4M-2932-1311

CONN DVI 29POS 1.5A DIGTL/ANALOG

XM7B-0442

CONN USB 1A 30VAC R/A WHITE

XOCLCC6EVB

EVAL BOARD FOR XOCLCC6

XR16M890IL32-0C-EB

BOARD EVAL XR16M890IL32

XR18W750/753-0B-EB

EVAL BOARD FOR XR18W750/753

相关代理商/技术参数

XGC

制造商:Excelsys Technologies 功能描述:Power Suply, 36V@5.6A, Open Frame, Cage Mount, Modular, UltiMod Series 制造商:Excelsys Technologies 功能描述:MODULE POWER 28.8V-39.6V 5.6A

XGC10-88-S20

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC10-88-S20 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC10-88-S20

XGC11-88-S20

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20

XGC11-88-S20Z1

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S20Z1

XGC11-88-S40

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC11-88-S40

XGC12-81Z1

制造商:Johnson Electric / Saia-Burgess 功能描述:Catalogue / XGC12-81Z1

XGC12-88

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88

XGC12-88-J23

制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XGC12-88-J23